| Deletions are marked like this. | Additions are marked like this. |

| Line 8: | Line 8: |

|

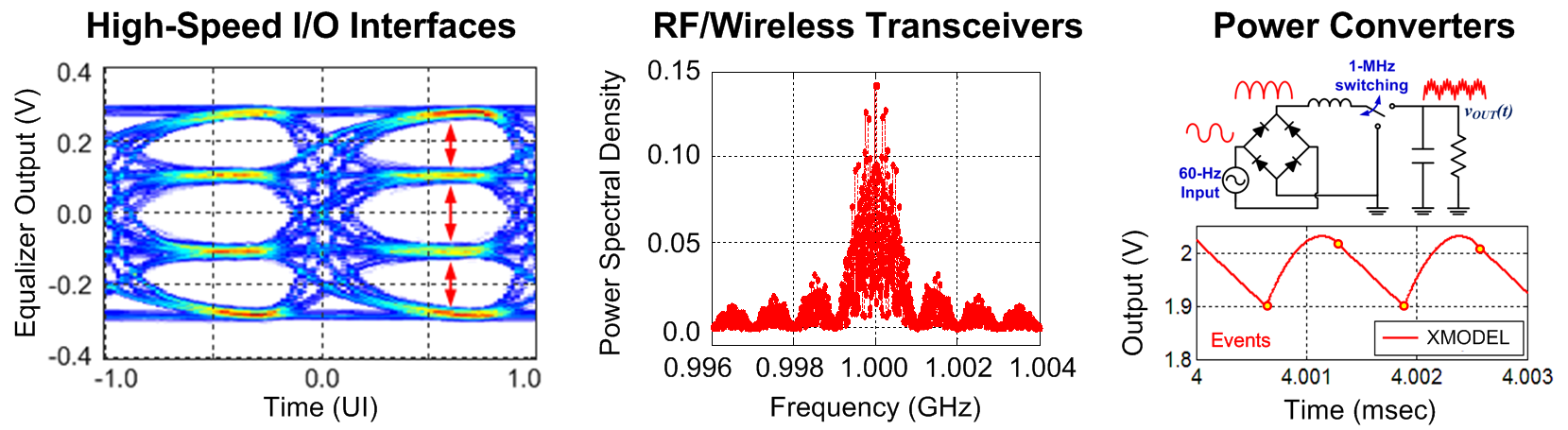

= IC Design and Verification Tools Developed by MICS = == XMODEL: A Fast Behavioral Simulator for Analog/Mixed-Signal Systems == XMODEL is an extension to SystemVerilog simulators including Synopsys VCS, MentorGraphics ModelSim and Cadence NC-Verilog that enables accurate functional modeling and fast simulation of analog/mixed-signal systems. For high-speed links, XMODEL also provides powerful statistical simulation capability that can estimate extremely low bit-error rate (BER) of 10^-12 within a few minutes. For more information, please visit http://mics.snu.ac.kr/xmodel. {{attachment:xmodel_image.jpg}} |

|

| Line 14: | Line 22: |

| = Verilog-A Modules for Variable Domain Transformation = | == Verilog-A Modules for Variable Domain Transformation == |

Contents

IC Design and Verification Tools Developed by MICS

XMODEL: A Fast Behavioral Simulator for Analog/Mixed-Signal Systems

XMODEL is an extension to SystemVerilog simulators including Synopsys VCS, MentorGraphics ModelSim and Cadence NC-Verilog that enables accurate functional modeling and fast simulation of analog/mixed-signal systems. For high-speed links, XMODEL also provides powerful statistical simulation capability that can estimate extremely low bit-error rate (BER) of 10^-12 within a few minutes. For more information, please visit http://mics.snu.ac.kr/xmodel.

Verilog-A Modules for Variable Domain Transformation

Tags: software