| Deletions are marked like this. | Additions are marked like this. |

| Line 19: | Line 19: |

| ||<style="border:none;text-align:left;vertical-align:top;">Many modern mixed-signal systems such as phase/delay-locked loops and DC-DC converters exhibit global convergence failures, also known as start-up failures. In other words, the system may have intermittent start-up failures due to its poorly initialized states. For instance, an oscillator may not start, a PLL may not converge to lock, and a DC-DC converter may fail to provide a correct voltage. To verify the existence of global convergence failures, GCAT offers two complementary approaches: the cluster split detection and indeterminate state (‘X’) elimination algorithms. For details, please visit [[http://mics.snu.ac.kr/wiki/GCAT|this page]]. ||<style="border:none;vertical-align:top;">{{attachment:gcat_image.jpg|Global Convergence Analysis Toolkit|width=30%}}|| | ||<style="border:none;text-align:left;vertical-align:top;">Many modern mixed-signal systems such as phase/delay-locked loops and DC-DC converters exhibit global convergence failures, also known as start-up failures. In other words, the system may have intermittent start-up failures due to its poorly initialized states. For instance, an oscillator may not start, a PLL may not converge to lock, and a DC-DC converter may fail to provide a correct voltage. To verify the existence of global convergence failures, GCAT offers two complementary approaches: the cluster split detection and indeterminate state (‘X’) elimination algorithms. For details, please visit [[http://mics.snu.ac.kr/wiki/GCAT|this page]]. ||<style="border:none;vertical-align:top;">{{attachment:gcat_image.jpg|Global Convergence Analysis Toolkit|width=300}}|| |

| Line 29: | Line 29: |

|

|

Contents

IC Design and Verification Tools Developed by MICS

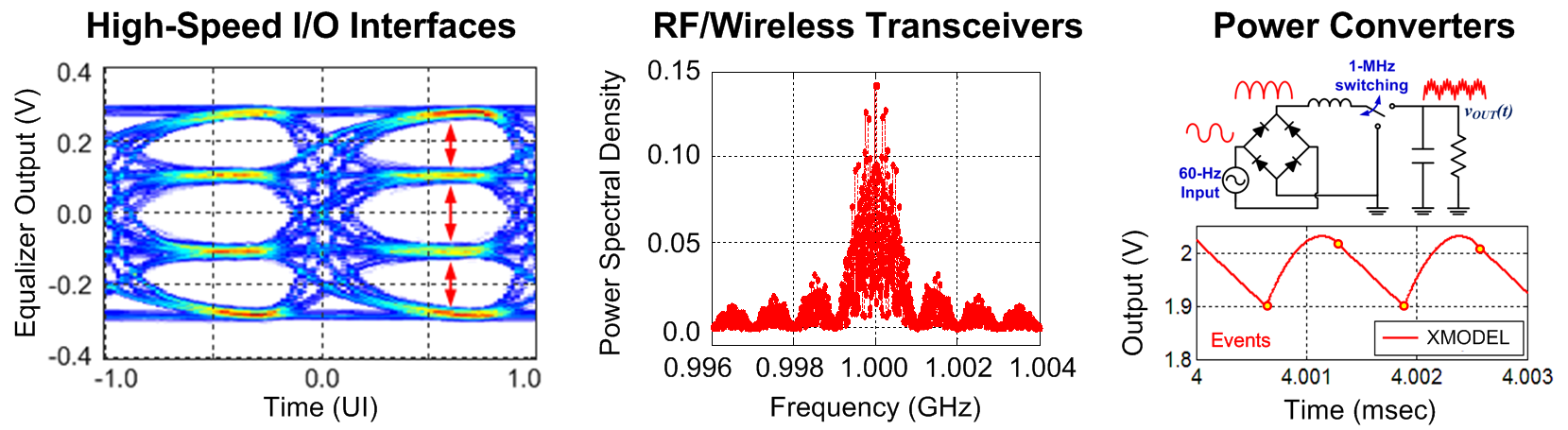

XMODEL: A Fast Behavioral Simulator for Analog/Mixed-Signal Systems

XMODEL is an extension to SystemVerilog simulators including Synopsys VCS, MentorGraphics ModelSim and Cadence NC-Verilog that enables accurate functional modeling and fast simulation of analog/mixed-signal systems. For high-speed links, XMODEL also provides powerful statistical simulation capability that can estimate extremely low bit-error rate (BER) of 10^-12 within a few minutes. For more information, please visit http://mics.snu.ac.kr/xmodel.

Global Convergence Analysis Toolkit (GCAT)

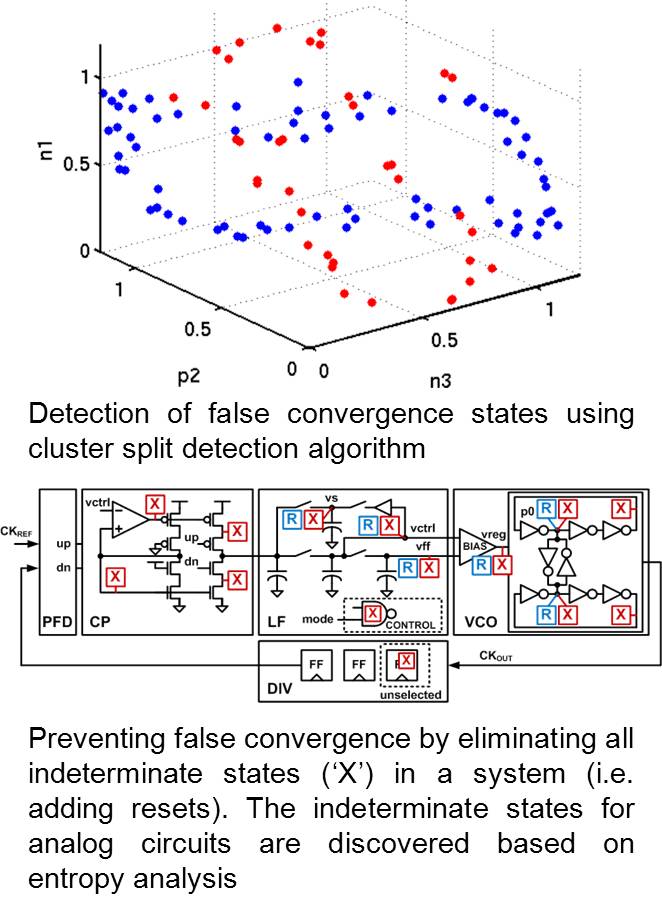

Many modern mixed-signal systems such as phase/delay-locked loops and DC-DC converters exhibit global convergence failures, also known as start-up failures. In other words, the system may have intermittent start-up failures due to its poorly initialized states. For instance, an oscillator may not start, a PLL may not converge to lock, and a DC-DC converter may fail to provide a correct voltage. To verify the existence of global convergence failures, GCAT offers two complementary approaches: the cluster split detection and indeterminate state (‘X’) elimination algorithms. For details, please visit this page. |

|

- Ref: S. Youn, J. Kim, M. A. Horowitz, "Global Convergence Analysis of Mixed-Signal Systems", ACM/IEEE Design Automation Conf. (DAC), June 2011.

Ref: S. Youn and J. Kim, "Preventing Global Convergence Failure in Mixed-Signal Systems via Indeterminate State (‘X’) Elimination," IEEE Trans. Circuits and Systems I, 2013. (doi)

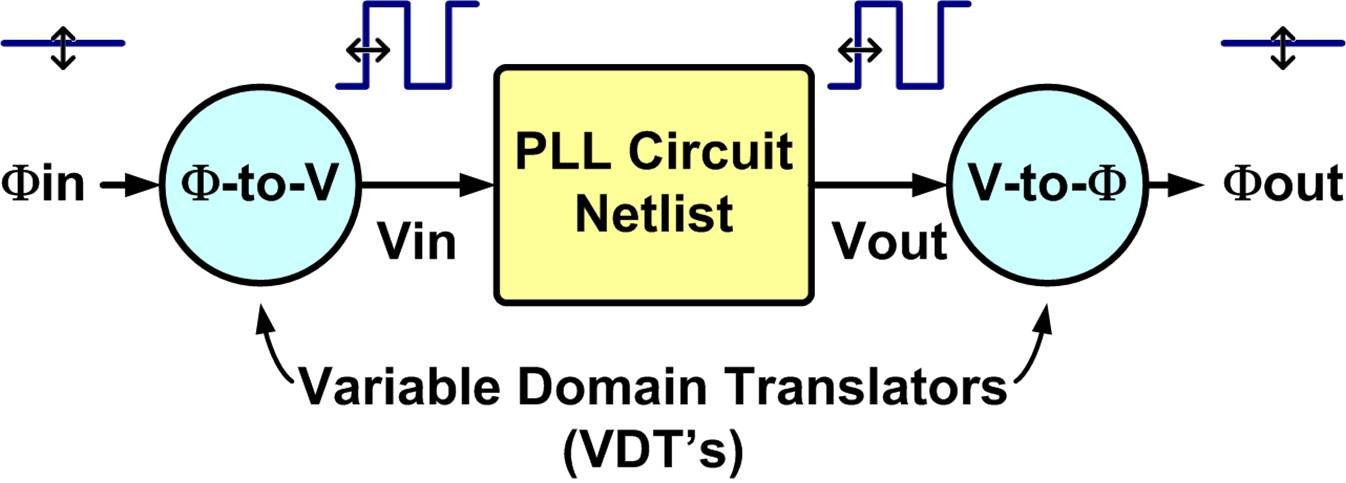

Verilog-A Modules for Variable Domain Transformation

Variable Domain Transformation (VDT) is a useful concept to convert a seemingly nonlinear system in one variable domain into a linear system in another one. For instance, a phase-locked loop (PLL) that takes a large-signal clock input and produces a large-signal clock output may be viewed as a strongly-nonlinear system in voltage domain, but most PLL designers want to view it as a linear system in phase domain. With VDT modules, one can perform a periodic AC analysis (PAC) in variable domains other than voltage or current, such as phase, frequency, delay, and duty-cycle in order to simulate the AC transfer function of a phase-locked loop, delay-locked loop, duty-cycle adjuster.

Ref: J. Kim, K. D. Jones, M. A. Horowitz, ʺVariable Domain Transformation for Linear PAC Analysis of Mixed‐Signal Systems,ʺ ACM/IEEE Int’l Conf. on Computer‐Aided Design (ICCAD), Nov. 2007 (doi).

VDT module package: vdt.tar.gz